## FlexSense® I-Series Programmable Incremental Encoder

### FS210/FS310 Datasheet

#### Description:

The FS210/FS310 contains a revolutionary optical sensor array that can be programmed to operate with a wide range of codewheel diameters, including linear strips, and resolutions. This programmable sensor is packaged standalone in a compact Opto-QFN package for the FS210, and a near-IR LED is combined with the sensor in the same package for the FS310. With unparalleled flexibility and versatility in a robust, subcompact package, with closed-loop LED driver control, with on-chip interpolation, and with support for automated alignment and configuration, the FlexSense™ products redefine flexibility.

#### How we help you:

- Accelerate time-to-market by reducing engineering cost and effort

- Reduce portfolio complexity with a "one-size-fits-many" solution

- Increase manufacturing throughput and cost efficiency

- Promote product innovation

FS210

Near-IR LED Chip

#### Features and Benefits:

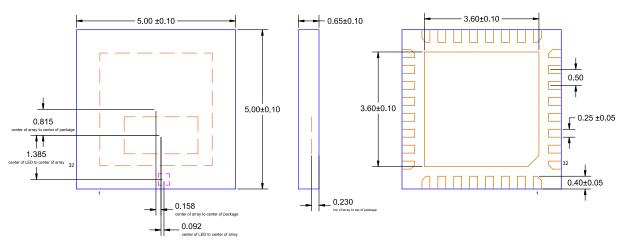

- Incremental optical encoder sensor IC in 32-pin 5mm x 5mm x 0.65mm OQFN package

- Both transmissive (FS210) and reflective (FS310) variants available.

- User-programmable, high-resolution photosensor pixel array enables quick customization and improves time-to-market.

- Customizable quadrature- and index-track dimensions

- Analog or digital quadrature-track output

- Compatible with code-wheel resolution of up to 1,200 lines per inch, or 4,096 PPR at a 15mm optical radius

- Programmable auto-configuration simplifies assembly and alignment.

- Closed-loop LED drive control

- IR LED embedded in the same package (FS310 only)

- Diagnostic functionality:

- High-temperature fault (with interrupt signaling feedback)

- LED-drive control loop out of regulation (with interrupt signaling feedback)

- Power-on reset (with interrupt signaling feedback)

- Code-wheel eccentricity

- I<sup>2</sup>C interface

- -40°C to +125°C ambient operating temperature

- On-chip quad-track interpolation (2x, 4x, 8x) and division (by powers of 2 up to 2,048)

- Quad-track output characteristics at native frequency up to 400kHz:

- o THD ≤ 1.0% on analog outputs

- Transient noise ≤ 1.0% of signal amplitude on analog outputs at 40mW/cm2 input power density

- Angular position accuracy ±1 part in 100K, or about 12 arc-seconds at 1,500 PPR, on digital outputs

- Single-supply (3.3V ± 10%) operation

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **General Description**

The FS210/FS310 is a user-configurable single-chip solution for an incremental optical encoder, available in a surface-mount high-usage-temperature-tolerant package. The sensor is available for both transmissive (FS210) and reflective (FS310) applications. Its programmable photosensor pattern can accommodate code wheels with printing densities of up to 1,200 lines per inch, which corresponds to more than 4,096 pulses per revolution (PPR) at an optical radius of 15mm. It provides complementary quadrature—and index-track outputs. Its quadrature outputs are configurable as either analog (with  $\leq$  1% THD, enabling high-quality off-chip interpolation) or digital (with low quadrature error) with up to 8x interpolation or programmable down-division by up to 2,048x in order to handle a wider logical PPR range. Its digital index-track output can be configured to be synchronized to either quadrature output, for a pulse width of exactly one-half cycle, or to both quadrature outputs, for a pulse width of exactly one-quarter cycle. The FS310 includes an in-package LED, and both the FS210/FS310 include an integrated driver that is user-configurable either to drive a fixed user-configurable current or as part of a closed-loop control system to produce a fixed optical input power density over its photosensors. The easy-to-use I²C interface and memory-mapped photosensor configuration enable automated alignment and signal conditioning during encoder module assembly, all from a single 3.3V  $\pm$ 10% supply.

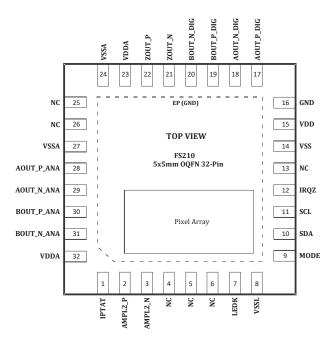

### **Package Pinout**

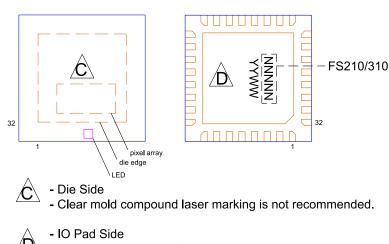

**Figure 1:** FS210 Pin Configuration (5mm x 5mm OQFN - top view)

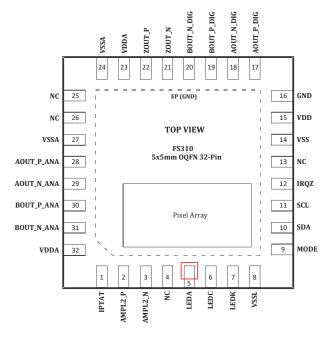

Figure 2: FS310 Pin Configuration (5mm x 5mm OQFN - top view)

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Pin Descriptions**

Table 1: Pin Description

| Pin Number    | Pin Name            | Description                                                                                                                     |

|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1             | IPTAT               | Analog temperature-sense current output:                                                                                        |

|               |                     | [0x88D] bits <5:4> = 11b: Current sunk (into the pin) is proportional to                                                        |

|               |                     | absolute temperature.                                                                                                           |

| 2.2           | AAADI 2. D          | [0x88D] bits <5:4> = 00b: Output is floating.                                                                                   |

| 2, 3          | AMPL2_P,<br>AMPL2_N | Analog amplitude-check voltage differential output:  [0x88D] bits <5:4> = 11b: Difference of two pin voltages is the sum of the |

|               | AIVIF LZ_IV         | squares of the A and B quadrature amplitudes.                                                                                   |

|               |                     | [0x88D] bits <5:4> = 00b: Outputs are floating.                                                                                 |

| 4, 13, 25, 26 | DNC                 | DO NOT CONNECT                                                                                                                  |

| 5             | DNC/LEDA            | LED anode (must connect off-chip to VDDA), FS310 only                                                                           |

| 6             | DNC/LEDC            | LED cathode (must connect to LEDK), FS310 only                                                                                  |

| 7             | LEDK                | LED drive current source (must connect to LEDC on FS310)                                                                        |

| 8             | VSSL                | Ground return for LED drive current                                                                                             |

| 9             | MODE                | Digital input to select between I <sup>2</sup> C master or slave setting at power-up:                                           |

|               |                     | <u>Logic-0</u> : Slave mode selected                                                                                            |

|               |                     | <u>Logic-1:</u> Master mode selected                                                                                            |

| 10            | SDA                 | Open-drain I <sup>2</sup> C data                                                                                                |

| 11            | SCL                 | Open-drain I <sup>2</sup> C clock                                                                                               |

| 12            | IRQZ                | Open-drain system interrupt output                                                                                              |

| 14, 16        | VSS                 | Digital ground connection (must connect to both at board level)                                                                 |

| 15            | VDD                 | Digital positive voltage supply                                                                                                 |

| 17            | AOUT_P_DIG          | Digital quadrature-track positive-sense A (cosine) output                                                                       |

| 18            | AOUT_N_DIG          | Digital quadrature-track negative-sense A (cosine) output                                                                       |

| 19            | BOUT_P_DIG          | Digital quadrature-track positive-sense B (sine) output                                                                         |

| 20            | BOUT_N_DIG          | Digital quadrature-track negative-sense B (sine) output                                                                         |

| 21            | ZOUT_N              | Digital negative-sense index-track output                                                                                       |

| 22            | ZOUT_P              | Digital positive-sense Index track output                                                                                       |

| 23            | VDDA                | Analog positive voltage supply                                                                                                  |

| 24, 27        | VSSA                | Analog ground connection (must connect to both at board level)                                                                  |

| 28            | AOUT_P_ANA          | Analog quadrature-track positive-sense A (cosine) output                                                                        |

| 29            | AOUT_N_ANA          | Analog quadrature-track negative-sense A (cosine) output                                                                        |

| 30            | BOUT_P_ANA          | Analog quadrature-track positive-sense B (sine) output                                                                          |

| 31            | BOUT_N_ANA          | Analog quadrature-track negative-sense B (sine) output                                                                          |

| 32            | VDDA                | Analog positive voltage supply                                                                                                  |

| EP_GND        | VSS                 | Exposed backside thermal pad (must connect to pins 14, 16 at board level)                                                       |

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Absolute Maximum Ratings**

Table 2: Absolute Maximum Ratings1

| Characteristic                                                                                                       | Min   | Max  | Unit   |

|----------------------------------------------------------------------------------------------------------------------|-------|------|--------|

| Storage Temperature                                                                                                  | -55   | 135  | °C     |

| Operating Temperature                                                                                                | -40   | 125  | °C     |

| Potential difference between any two pins of the same net (VSS, VSSA, LEDK)                                          | -0.05 | 0.05 | V      |

| Potential difference between VDD and VDDA pins                                                                       | -0.5  | 0.5  | V      |

| Potential difference between any two of VSS, VSSA, and VSSL                                                          | -0.05 | 0.05 | V      |

| Potential on (VDD, VDDA or LEDA) pin with respect to (VSS, VSSA, or VSSL) pin                                        | -0.5  | 5.0  | V      |

| Potential on any other pin with respect to VSS, VSSA, or VSSL pin                                                    | -0.5  | 5.0  | V      |

| Potential on any other pin with respect to VDD or VDDA pin                                                           | -5.0  | 0.5  | V      |

| Current into/out of VDD, VDDA, VSS, or VSSA pin                                                                      | -50   | 50   | mA     |

| Current into/out of LEDA, LEDK, or VSSL pin                                                                          | -100  | 100  | mA     |

| Current into/out of any analog quadrature-track output pin (AOUT_P_ANA, AOUT_N_ANA, BOUT_P_ANA, or BOUT_N_ANA)       | -5    | 5    | mA     |

| Current into/out of any other pin                                                                                    | -25   | 25   | mA     |

| Incident optical power density                                                                                       |       | 50   | mW/cm² |

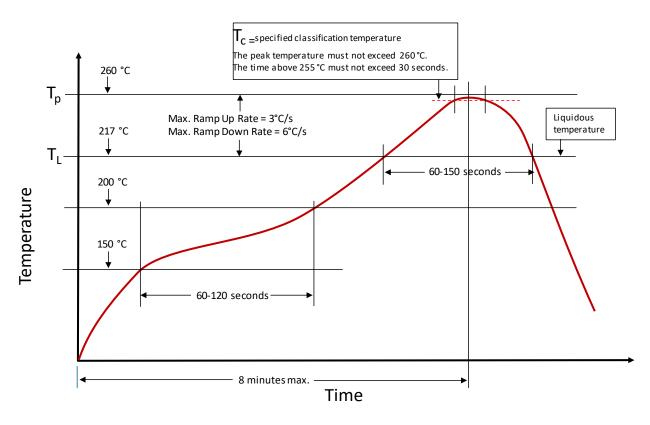

| Reflow temperature, MSL-6 (5 seconds or less at this temperature; 40 seconds or less within 5°C of this temperature) |       | 260  | °C     |

| Electrostatic discharge immunity (HBM)                                                                               | ±4    |      | kV     |

Functional and testing operating conditions given in Table 3. Absolute Maximum Ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Prolonged operation of the device at these conditions may result in permanent damage to the device.

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Electrical/Optical Characteristics**

**Table 3.** Electrical and Optical Operating Characteristics.

| Characteristic                          | Symbol                             | Conditions                                                     | Min      | Тур    | Max      | Unit     | Notes    |

|-----------------------------------------|------------------------------------|----------------------------------------------------------------|----------|--------|----------|----------|----------|

| GENERAL CHARACTERISTICS                 |                                    |                                                                |          |        |          | l        | <u> </u> |

| Ambient temperature                     | T <sub>A</sub>                     |                                                                | -40      | -      | 125      | °C       | 1        |

| Thermal shutdown trip point             | T <sub>jSL</sub>                   |                                                                | 135      | 150    | 170      | °C       | 2        |

| Thermal alarm trip point                | $T_{jAL}$                          | X = TALM<3:0>                                                  | 195-9.5X | 200-9X | 205-8.5X | °C       | 3        |

| Supply voltage                          | V <sub>DD</sub> , V <sub>DDA</sub> |                                                                | 2.97     | 3.30   | 3.60     | V        | 4        |

| Supply voltage power-up time            | t <sub>PU</sub>                    | From 0.1V to (V <sub>DDA</sub> , V <sub>DD</sub> – 0.1V)       | 100      |        |          | us       |          |

| Wake-up time                            | twu                                | MODE = 0                                                       |          | 2.5    |          | ms       |          |

|                                         |                                    | MODE = 1                                                       |          | 95.5   |          | ms       |          |

| Active current (analog)                 | I <sub>DDA</sub>                   | QCFG=0x00; f=1kHz                                              |          | 9.0    | 12.0     | mA       | 4, 5     |

| Active current (digital)                | I <sub>DD</sub>                    | QCFG=0x13; f=1kHz                                              |          | 2.0    |          | mA       | 4, 5     |

| PHOTODIODES                             | <u> </u>                           |                                                                |          |        | ı        | <u>I</u> | <u> </u> |

| Wavelength of incident power            | λ                                  |                                                                | 400      |        | 950      | nm       |          |

| QUADRATURE-TRACK DIGITAL                | L CHARACT                          | ERISTICS                                                       |          |        |          | l        |          |

| Output high current                     | I <sub>OH:QD</sub>                 | QCFG<4> = 1; V <sub>OH</sub> = V <sub>DD</sub> - 0.4V          |          | -15    |          | mA       | 6        |

| Output low current                      | I <sub>OL:QD</sub>                 | QCFG<4> = 1; V <sub>OL</sub> = 0.4V                            |          | 28     |          | mA       |          |

| Output high short-circuit current limit | I <sub>OHL:QD</sub>                | QCFG<4> = 1; Pin shorted to VSS                                |          | -50    |          | mA       | 6        |

| Output low short-circuit current limit  | I <sub>OLL:QD</sub>                | QCFG<4> = 1; Pin shorted to V <sub>DD</sub>                    |          | 90     |          | mA       |          |

| Output extrinsic fall time              | t <sub>F:Q</sub>                   | QCFG<4>=1; C <sub>L</sub> =20pF; 90% to 10% of V <sub>DD</sub> |          | 10     |          | ns       |          |

| Output extrinsic rise time              | t <sub>R:Q</sub>                   | QCFG<4>=1; C <sub>L</sub> =20pF; 10% to 90% of V <sub>DD</sub> |          | 10     |          | ns       |          |

| Digital phase error                     | $\epsilon_{\phi}$                  | 1σ; f≤100kHz; QCFG=0x10 (1x interpolation)                     |          | 0.4    |          | ۰        | 5, 7, 8, |

|                                         |                                    | 1σ; f≤100kHz; QCFG=0x13 (8x interpolation)                     |          | 7.5    |          |          | 9        |

| Duty cycle variation                    | $\Delta D_{\mathrm{Q}}$            | 1σ; f≤100kHz; QCFG=0x10 (1x interpolation)                     |          | 0.2    |          | %        | 5, 8, 9  |

|                                         |                                    | 1σ; f≤100kHz; QCFG=0x13 (8x interpolation)                     |          | 2      |          | %        |          |

| Period jitter                           | Δτ <sub>Ρ</sub> /τ                 | 1σ; f≤100kHz; QCFG=0x10 (1x interpolation)                     |          | 0.2    |          | %        | 5, 8, 9  |

|                                         |                                    | 1σ; f≤100kHz; QCFG=0x13 (8x interpolation)                     |          | 2      |          | %        |          |

| Cycle-to-cycle jitter                   | Δτ <sub>cc</sub> /τ                | 1σ; f≤100kHz; QCFG=0x10 (1x interpolation)                     |          | 0.3    |          | %        | 5, 8, 9  |

|                                         |                                    | 1σ; f≤100kHz; QCFG=0x13 (8x interpolation)                     |          | 3      |          | %        |          |

General Note

# FlexSense® I-Series Programmable Incremental Encoder

| Characteristic                              | Symbol Conditions   |                                                           | Min             | Тур  | Max                 | Unit | Notes    |

|---------------------------------------------|---------------------|-----------------------------------------------------------|-----------------|------|---------------------|------|----------|

| QUADRATURE-TRACK ANALO                      | G CHARAC            | TERISTICS                                                 |                 |      |                     |      |          |

| Output high short-circuit current limit     | I <sub>OHL:QA</sub> | QCFG<4> = 0; Pin shorted to VSS                           |                 | -1.2 |                     | mA   |          |

| Output low short-circuit current limit      | I <sub>OLL:QA</sub> | QCFG<4> = 0; Pin shorted to V <sub>DD</sub>               |                 | 2.5  |                     | mA   |          |

| Equivalent transimpedance gain              | Z <sub>Q:LN</sub>   | TQM2=0x00; ZCFG<6> = 1 (low noise)                        |                 | 2.9  |                     | ΜΩ   | 5, 8     |

| Input Frequency                             |                     | TQM2=0x00; ZCFG<6> = 1 (low noise)                        |                 |      | 400                 | kHz  | 5, 8     |

| Output common-mode voltage                  | V <sub>0:Q</sub>    | QCFG=0x00                                                 |                 | 1.25 |                     | V    | 5, 8     |

| Output noise voltage                        | V <sub>N:LN</sub>   | ZCFG<6> = 1; integrated over f ≤ 300kHz                   |                 | 2    |                     | mV   | 5, 8     |

|                                             | V <sub>N:HS</sub>   | ZCFG<6> = 1; integrated over f ≤ 3MHz                     |                 | 20   |                     | mV   |          |

| Total harmonic distortion                   | THDQ                | f≤100KHz                                                  |                 | -40  |                     | dB   | 5, 8     |

| INDEX TRACK CHARACTERISTI                   | CS                  | L                                                         |                 |      |                     |      |          |

| Output high current                         | I <sub>OH:Z</sub>   | V <sub>OH</sub> = V <sub>DD</sub> - 0.4V                  |                 | -15  |                     | mA   | 6        |

| Output low current                          | I <sub>OL:Z</sub>   | V <sub>OL</sub> = 0.4V                                    |                 | 28   |                     | mA   |          |

| Output high short-circuit current limit     | I <sub>OHL:Z</sub>  | Pin shorted to VSS                                        |                 | -50  |                     | mA   | 6        |

| Output low short-circuit current limit      | I <sub>OLL:Z</sub>  | Pin shorted to V <sub>DD</sub>                            |                 | 90   |                     | mA   |          |

| Output extrinsic fall time                  | t <sub>F:Z</sub>    | C <sub>L</sub> = 20pF; From 90% to 10% of V <sub>DD</sub> |                 | 10   |                     | ns   |          |

| Output extrinsic rise time                  | t <sub>R:Z</sub>    | C <sub>L</sub> = 20pF; From 10% to 90% of V <sub>DD</sub> |                 | 10   |                     | ns   |          |

| LED DRIVER CHARACTERISTICS                  | 5                   |                                                           |                 |      |                     |      |          |

| LEDK pin voltage                            | Vĸ                  | T <sub>A</sub> ≤ -40°C; I <sub>OL:K</sub> ≤ 85mA          | 0.60            |      |                     | V    |          |

|                                             |                     | T <sub>A</sub> ≤ 25°C; I <sub>OL:K</sub> ≤ 85mA           | 0.70            |      |                     |      |          |

|                                             |                     | T <sub>A</sub> ≤ 125°C; I <sub>OL:K</sub> ≤ 85mA          | 0.80            |      |                     |      |          |

| LEDK output current                         | I <sub>OL:K</sub>   | ILED = $0x00$ ; $V_{K(min)} \le V(LEDK) \le V_{K(max)}$   |                 | 0.1  | 10.0                | μΑ   | 10       |

|                                             |                     | ILED = 0x01; $V_{K(min)} \le V(LEDK) \le V_{K(max)}$      |                 | 0.60 |                     | mA   |          |

|                                             |                     | ILED = $0x7F$ ; $V_{K(min)} \le V(LEDK) \le V_{K(max)}$   |                 | 80   |                     | mA   |          |

| LEDK current differential non-<br>linearity | DNL <sub>I:K</sub>  | ILED<7> = 0; $V_{K(min)} \le V(LEDK) \le V_{K(max)}$      | -0.75           |      | 0.75                | LSB  | 11       |

| Closed-loop LED current update period       | t <sub>upd:N</sub>  | LEDLP<7> = 0; ILED<7> = 1                                 |                 | 16   |                     | S    |          |

| LED drive-alarm threshold                   | I <sub>OLA:K</sub>  |                                                           | 0.875*ILED<6:0> |      | mA                  |      |          |

| MODE PIN CHARACTERISTICS                    | I                   | <u> </u>                                                  | 1               |      |                     | I    | l        |

| Input low voltage                           | V <sub>IL:M</sub>   |                                                           |                 |      | 0.3*V <sub>DD</sub> | V    |          |

|                                             | l                   |                                                           | ı               |      |                     |      | <u> </u> |

General Note

TT Electronics reserves the right to make changes in product specification without notice or liability. All information is subject to TT Electronics' own data and is considered accurate at time of going to print.

# FlexSense® I-Series Programmable Incremental Encoder

| Characteristic                              | Symbol              | Conditions                                                                                                    | Min                 | Тур  | Max                 | Unit  | Notes    |

|---------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|-------|----------|

| Input high voltage                          | V <sub>IH:M</sub>   |                                                                                                               | 0.7*V <sub>DD</sub> |      |                     | V     |          |

| Input leakage current                       | I <sub>L:M</sub>    | OV ≤ V(pin) ≤ V <sub>DD</sub> , at 25°C                                                                       | -0.1                |      | 0.1                 | μΑ    |          |

| PREVENTIVE MAINENANCE OF                    | JTPUT CHA           | ARACTERISTICS                                                                                                 |                     |      |                     |       | l        |

| Proportional-to-absolute-                   | I <sub>PTAT</sub>   | T <sub>j</sub> = 25°C                                                                                         |                     | 10.4 |                     | μΑ    |          |

| temperature output current                  |                     | T <sub>j</sub> = 125°C                                                                                        |                     | 14.8 |                     | μΑ    |          |

| Wobble-detect coefficient                   | k <sub>W</sub>      |                                                                                                               |                     | 4    |                     | μA/V² |          |

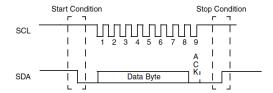

| I <sup>2</sup> C PIN CHARACTERISTICS        |                     |                                                                                                               |                     |      | 1                   |       | <u> </u> |

| Input low voltage                           | V <sub>IL</sub>     |                                                                                                               |                     |      | 0.3*V <sub>DD</sub> | V     |          |

| Input high voltage                          | V <sub>IH</sub>     |                                                                                                               | 0.7*V <sub>DD</sub> |      |                     | V     |          |

| Output low current                          | I <sub>OL</sub>     | V <sub>OL</sub> = 0.4V                                                                                        | 3                   |      |                     | mA    |          |

| Output fall time                            | tor                 | From V <sub>IH(min)</sub> to V <sub>IL(max)</sub>                                                             |                     |      | 250                 | ns    |          |

| Input capacitance                           | Cı                  | Presented by the device only                                                                                  |                     |      | 10                  | pF    |          |

| I <sup>2</sup> C MASTER/SYSTEM REQUIRE      | MENTS               |                                                                                                               | <u> </u>            |      |                     |       |          |

| SCL low time                                | t <sub>LOW</sub>    |                                                                                                               | 1.3                 |      |                     | μs    |          |

| SCL high time                               | t <sub>HIGH</sub>   |                                                                                                               | 0.6                 |      |                     | μs    |          |

| START-condition setup time                  | t <sub>SU;STA</sub> | $V_{SCL} \uparrow \rightarrow V_{SDA} \downarrow$                                                             | 0.6                 |      |                     | μs    |          |

| START-condition hold time                   | t <sub>HD;STA</sub> | $V_{SDA} \downarrow \rightarrow V_{SCL} \downarrow$                                                           | 0.6                 |      |                     | μs    |          |

| Data setup time                             | t <sub>su;dat</sub> | $V_{SDA} \updownarrow \rightarrow V_{SCL} \uparrow$ ; for bits being written from the master to this device   |                     |      | 100                 | μs    |          |

| Data hold time                              | t <sub>HD;DAT</sub> | $V_{SCL} \downarrow \rightarrow V_{SDA} \updownarrow$ ; for bits being written from the master to this device | 0                   |      |                     | μs    |          |

| Data valid wait time                        | t <sub>VD;DAT</sub> | $V_{SCL} \downarrow \rightarrow V_{SDA}$ valid; for bits being read from this device by the master            |                     |      | 0.9                 | μs    |          |

| STOP-condition setup time                   | t <sub>su;sto</sub> | $V_{SCL} \uparrow \rightarrow V_{SDA} \uparrow$                                                               | 0.6                 |      |                     | μs    |          |

| Bus free time (between STOP and next START) | t <sub>BUF</sub>    | $V_{SDA} \uparrow \rightarrow V_{SDA} \downarrow$                                                             | 1.3                 |      |                     | μs    |          |

| Total capacitance, each of SCL and SDA      | Св                  | Sum of on-chip (C <sub>i</sub> ) and off-chip capacitances                                                    |                     |      | 400                 | pF    |          |

<sup>&</sup>lt;sup>1</sup> Thermal self-heating must not increase junction temperature beyond 135°C in normal operation.

General Note

<sup>&</sup>lt;sup>2</sup> Tj > TjSL causes output drivers to be disabled, most on-chip static current consumption (LED driver, TIAs, interpolator) to be turned off, and the interrupt status bit INTR<4> to be set to 'b1. Additionally, it causes the IRQZ pin level to be driven to 'b0 if the interrupt mask bit INTR<0> is 'b1. Once the shutdown threshold is tripped, the part remains in shutdown until the user executes an I<sup>2</sup>C read access to the INTR register or until a power-on reset event occurs.

### FS210/FS310 Datasheet

- Tj > TjAL causes the interrupt status bit INTR<5> to be set to 'b1 and the IRQZ pin level to be driven to 'b0 if the interrupt mask bit INTR<1> is 'b1 but does NOT disable output drivers nor turn off on-chip static current consumption. Once the alarm threshold is tripped, the effects persist until the user executes an I<sup>2</sup>C read access to the INTR register or until a power-on reset event occurs.

- The specified supply current for a particular supply (VDD or VDDA) refers to the sum of the currents sunk by all pins connected to that supply since there are multiple pins for each supply.

- Configured to produce 1Vp-p quad-track analog voltages with as close zero differential DC offset as possible; low-noise mode (ZCFG<6> = 1) unless otherwise indicated.

- <sup>6</sup> Negative value implies current is flowing out of the pin.

- Assuming photocurrents are perfect sinusoids in perfect quadrature i.e. negligible THD attributable to non-ideality in pixel pattern or mechanical effects.

- Deviation from 90° of phase difference between differential A and B analog output voltages or between AOUT\_P\_DIG and BOUT\_P\_DIG.

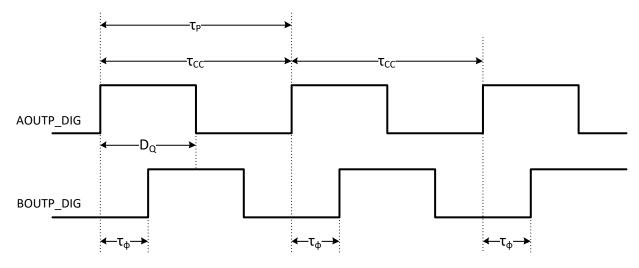

- 9 With reference to Figure 3

- Measurable only by placing a low-impedance current meter between LEDK and LEDC pins at the package level or by measuring the current into LEDA. Room temperature is assumed for typical conditions and 125°C is assumed for max conditions.

- 11 Nominal value of 1 LSB is 0.6mA.

Figure 3: Jitter specification diagram; with  $\tau_P$  as time period,  $\tau_{CC}$  as a similar time used to calculate cycle-to-cycle jitter,  $D_Q$  as the duty cycle, and  $\tau_{\Phi}$  as time of the phase difference between A and B. The phase error,  $\epsilon_{\Phi}$ , can be calculated as  $360(\tau_{\Phi}/\tau_P)$ .

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

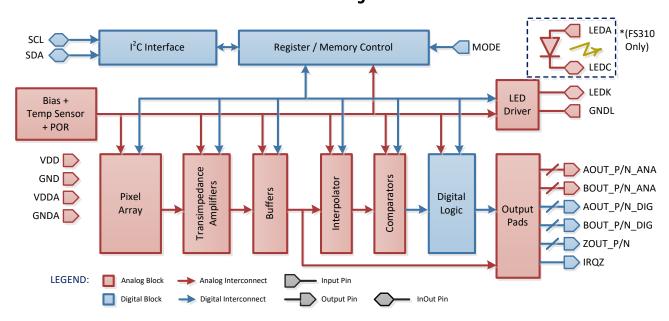

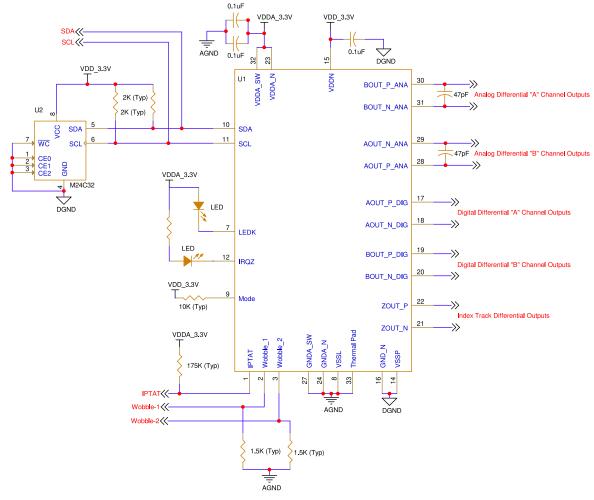

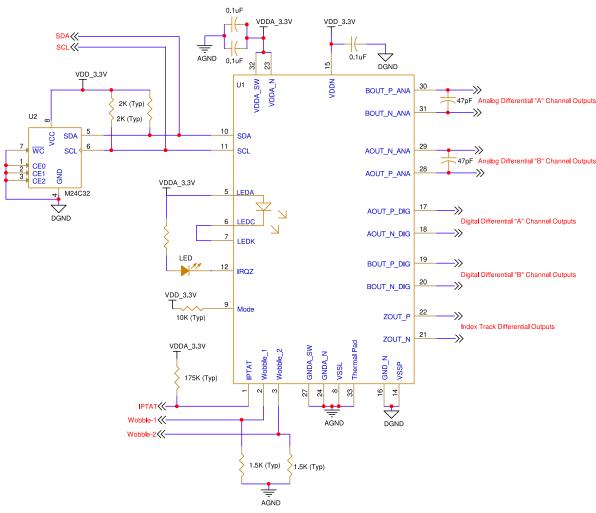

### **Block Diagram**

Figure 4: FS210/FS310 Block Diagram

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Memory Mapping**

Table 4: FS210/FS310 Memory Map

|                 | Power-On          |        |                                                                                                                                                                                   |

|-----------------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Range   | Reset State       | Regist | er                                                                                                                                                                                |

| 0x0000 – 0x01FF | <random></random> | PXC    | Pixel control bits                                                                                                                                                                |

| 0x0200 – 0x03FF | Х                 |        | <not implemented=""></not>                                                                                                                                                        |

| 0x0400 - 0x041F | <random></random> | CCFG   | Pixel column configuration bits                                                                                                                                                   |

| 0x0420 – 0x087F | Х                 |        | <not implemented=""></not>                                                                                                                                                        |

| 0x0880          | 0x00              | TDCA   | Offset trim for A (cosine) quadrature-track signal path                                                                                                                           |

| 0x0881          | 0x00              | TDCB   | Offset trim for B (sine) quadrature-track signal path                                                                                                                             |

| 0x0882          | 0x00              | TQM1   | Trim to equalize A and B quadrature-track differential output voltage magnitudes                                                                                                  |

| 0x0883          | 0x00              | TQM2   | Trim to change A and B quadrature-track differential buffer gains together                                                                                                        |

| 0x0884          | 0x00              | QCFG   | Quadrature-track output control                                                                                                                                                   |

| 0x0885          | 0x00              | ZCFG   | Index-track output control                                                                                                                                                        |

| 0x0886          | 0x10              | ILED   | LED drive-current open-/closed-loop selection and maximum current magnitude                                                                                                       |

| 0x0887          | 0x26              | LEDLP  | Control bits for closed-loop LED drive control                                                                                                                                    |

| 0x0888          | 0xCC              | TALM   | Thermal-alarm trip point selection thermal-shutdown/alarm trim                                                                                                                    |

| 0x0889          | 0x00              | INTR   | Interrupt mask and status bits                                                                                                                                                    |

| 0x088A          | 0xFF              | TIAE   | Enable bits for quadrature-track and index-track transimpedance amplifiers                                                                                                        |

| 0x088B          | 0x00              | CBFEZ  | Enable bits (active-low) for quadrature-track buffers and quadrature- and indextrack comparators                                                                                  |

| 0x088C          | 0x00              | SIG    | Signature: off-chip NVM should be set up such that master-mode power-up sequence writes 0xAA to this register                                                                     |

| 0x088D          | 0x01              | MISC   | Control bits to output PTAT current and Sin <sup>2</sup> x + Cos <sup>2</sup> x differential currents                                                                             |

| 0x088E          | 0x00 or 0xAA      | SIGV   | Signature-verify register (read-only): reads 0x0A if a master-mode power-up sequence completes successfully and 0xAA was copied to SIG during this sequence; reads 0x00 otherwise |

| 0x088F          | 0x10              | LEDLV  | Actual instantaneous LED drive current (read-only)                                                                                                                                |

## FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Pixel Array Control**

Correct operation of the FS210/FS310 requires that its photoactive area, an array of 4,096 pixels (64 rows by 64 columns), be configured to be consistent with the code wheel with which it is being used. Six aggregate photocurrents are produced by the device's photoactive area: the positive- and negative-sense photocurrents for the two quadrature-track outputs and for the index-track output. Each pixel's photocurrent either contributes to one of the six aggregate photocurrents (A+, A-, B+, Z+, Z-) or is shunted to ground, depending on how the pixel is configured.

The on-chip physical dimensions of each pixel are  $36.2\mu m$  by  $18.1\mu m$ , so the dimensions of the entire photoactive area are 2.32mm by 1.16mm.

Associated with each pixel is a single SRAM bit called a **Pixel Control (PXC)** bit, and associated with each pixel column are four SRAM bits called a **Column Configuration (CCFG)** nibble. A column's CCFG nibble selects the aggregate photocurrent output to which the active pixels in that column contribute (A+, A-, B+, B-, Z+, Z-, or none). A pixel's PXC bit controls whether that pixel is *active* – i.e. its photocurrent contributes to the aggregate photocurrent output selected by the column's 4-bit control field – or *inactive* – i.e. its photocurrent is shunted to ground.

The 4,096 PXC bits, or 512 bytes, occupy the address range [0x000 - 0x1FF]. The 64 CCFG nibbles, or 32 bytes, occupy the address range [0x400 - 0x41F]. The mapping of logical bytes and bits to physical columns and pixels is detailed below.

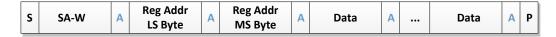

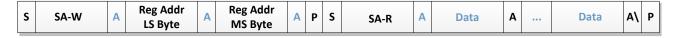

The PXC and CCFG bytes are volatile SRAM, so their contents are lost every time the device is power cycled. Therefore, the desired contents must be stored off-chip in non-volatile storage somewhere in the system, and the system must contain a means to copy the patterns from the off-chip non-volatile storage into the on-chip SRAM through the device's I<sup>2</sup>C port every time it is powered up. If the system contains a microcontroller with non-volatile storage outside the encoder module, then this microcontroller can contain the non-volatized PXC and CCFG contents. If the system does not contain a microcontroller with non-volatile storage outside the encoder module, then a non-volatile memory chip with an I<sup>2</sup>C interface and at least 1Kbyte capacity, such as the M24C32S-FCU from ST, is required.

Table 5: Mapping of PXC and CCFG Registers to Pixel Location

|               | Col. Grp. 000        | Col. Grp. 100        | Col. Grp. 001        | Col. Grp. 101        | Col. Grp. 010        | Col. Grp. 110        | Col. Grp. 011        | Col. Grp. 111        |

|---------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Row 00        | [0x0000]             | [0x0004]             | [0x0001]             | [0x0005]             | [0x0002]             | [0x0006]             | [0x0003]             | [0x0007]             |

| Row 01        | [8000x0]             | [0x000C]             | [0x0009]             | [0x000D]             | [0x000A]             | [0x000E]             | [0x000B]             | [0x000F]             |

| Row 02        | [0x0010]             | [0x0014]             | [0x0011]             | [0x0015]             | [0x0012]             | [0x0016]             | [0x0013]             | [0x0017]             |

| Row 03        | [0x0018]             | [0x001C]             | [0x0019]             | [0x001D]             | [0x001A]             | [0x001E]             | [0x001B]             | [0x001F]             |

| Rows<br>04-59 |                      |                      |                      |                      |                      |                      |                      |                      |

| Row 60        | [0x01E0]             | [0x01E4]             | [0x01E1]             | [0x01E5]             | [0x01E2]             | [0x01E6]             | [0x01E3]             | [0x01E7]             |

| Row 61        | [0x01E8]             | [0x01EC]             | [0x01E9]             | [0x01ED]             | [0x01EA]             | [0x01EE]             | [0x01EB]             | [0x01EF]             |

| Row 62        | [0x01F0]             | [0x01F4]             | [0x01F1]             | [0x01F5]             | [0x01F2]             | [0x01F6]             | [0x01F3]             | [0x01F7]             |

| Row 63        | [0x01F8]             | [0x01FC]             | [0x01F9]             | [0x01FD]             | [0x01FA]             | [0x01FE]             | [0x01FB]             | [0x01FF]             |

| •             |                      |                      |                      |                      |                      |                      |                      |                      |

| CCFG          | [0x0400 –<br>0x0403] | [0x0404 –<br>0x0407] | [0x0408 –<br>0x040B] | [0x040C –<br>0x040F] | [0x0410 –<br>0x0413] | [0x0414 –<br>0x0417] | [0x0418 –<br>0x041B] | [0x041C –<br>0x041F] |

General Note

## FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

#### Pixel Control Registers (PXC: [0x0000 - 0x01FF])

The mapping of pixels to the PXC bits that control them is as follows: The 64 rows in the pixel array are numbered consecutively, from row 00 at the top to row 63 at the bottom. The 64 columns in the pixel array are divided into eight groups of eight contiguous columns. The column groups are numbered non-consecutively: group 0 contains the leftmost 8 columns, group 4 contains the next-leftmost 8 columns, group 1 contains the next-leftmost 8 columns, then group 5, then group 2, then group 6; group 3 contains the second-rightmost 8 columns, and group 7 contains the rightmost 8 columns. The address of the PXC register that controls a particular set of 8 pixels is found by concatenating the row number (6 bits) and the column group number (3 bits) of the set of pixels, as shown below:

Table 6. PXC Register Address

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4 | 3 | 2  | 1        | 0          |

|----|----|----|----|----|----|---|---|---|-----|-----|---|---|----|----------|------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 |   |   | Rov | w # |   |   | Со | l. Group | <b>)</b> # |

A single PXC register controls 8 pixels, with the bits from least-significant to most-significant controlling the pixels in the set of 8 from left to right: the least-significant bit controls the leftmost pixel of the 8, and the most-significant bit controls the rightmost pixel of the 8. If the value of the PXC register bit controlling a particular pixel is 1, then the photocurrent of that pixel does contribute to the aggregated output current to which the column is assigned by its CCFG register. If the value of the PXC register bit controlling a particular pixel is 0, then the photocurrent of that pixel is shunted to ground and does not contribute to the aggregated output current to which the column is assigned by its CCFG register.

Table 7. Bits Within a PXC Register

| MSB       | Bit 6              | Bit 5              | Bit 4              | Bit 3             | Bit 2             | Bit 1             | LSB      |

|-----------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|----------|

| Rightmost | 2 <sup>nd</sup> -  | 3 <sup>rd</sup> -  | 4 <sup>th</sup> -  | 4 <sup>th</sup> - | 3 <sup>rd</sup> - | 2 <sup>nd</sup> - | Leftmost |

| pixel     | rightmost<br>pixel | rightmost<br>pixel | rightmost<br>pixel | leftmost<br>pixel | leftmost<br>pixel | leftmost<br>pixel | pixel    |

#### Column Configuration Registers (CCFG: [0x0400 - 0x041F])

Each CCFG register controls two adjacent pixel columns: the four least-significant bits control the leftmost of the two columns, and the four most-significant bits control the rightmost of the two columns. The column pairs controlled by individual CCFG registers step from left to right with increasing address: [0x0400] controls the leftmost pair of columns, [0x0401] controls the second-leftmost pair, [0x041E] controls the second-rightmost pair, and [0x041F] controls the rightmost pair. The value of each nibble in a CCFG register selects the aggregated photocurrent (A+, A-, B+, B-, Z+, Z-) to which the photocurrents from all "ON" pixels in the corresponding column contribute, according to the table below.

Table 8. CCFG Byte

| MSB | Bit 6        | Bit 5         | Bit 4 | Bit 3 | Bit 2       | Bit 1        | LSB |

|-----|--------------|---------------|-------|-------|-------------|--------------|-----|

|     | Rightmost co | olumn of pair |       |       | Leftmost co | lumn of pair |     |

General Note

© TT electronics plc

TT Electronics | OPTEK Technology 2900 Plano Pkwy, Plano, TX 75074 | Ph: +1 972 323 2200 www.ttelectronics.com | sensors@ttelectronics.com

TT Electronics reserves the right to make changes in product specification without notice or liability. All information is subject to TT Electronics' own data and is considered accurate at time of going to print.

Rev B, 3/25/2021 Page 12

## FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

Table 9. CCFG Nibble Mapping

| CCFG<br>Nibble | Aggregated<br>Photocurrent |

|----------------|----------------------------|

| 'b0000         | A+                         |

| 'b0001         | A-                         |

| 'b0010         | B+                         |

| 'b0011         | B-                         |

| 'b0100         | Z+                         |

| 'b0101         | Z-                         |

| All Others     | Shunted to Ground          |

Throughout the remainder of this document, it is assumed that the FlexSense™ is mounted in a rotary encoder system, that its PXC and CCFG registers have been populated to be consistent with the code wheel in that system, and that the code wheel is rotating with constant angular velocity. The direction of rotation is a matter of convention. Given a PXC/CCFG data pattern designed to produce A-leading-B quadrature-track outputs under clockwise code-wheel rotation and B-leading-A outputs under counter-clockwise rotation, it is straightforward to modify the pattern to produce A-leading-B outputs under counter-clockwise rotation and B-leading-A outputs under clockwise rotation. The illustrative figures below assume that the combination of the PXC/CCFG data pattern and the direction of code-wheel rotation produces A-leading-B quadrature-track output signals.

## FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Quadrature-Track Outputs**

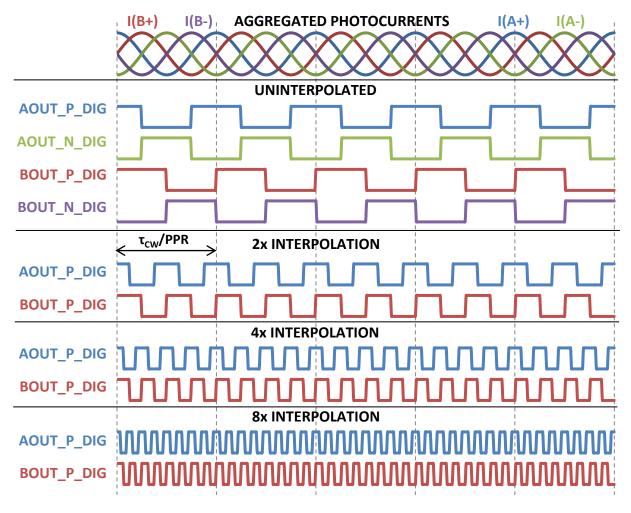

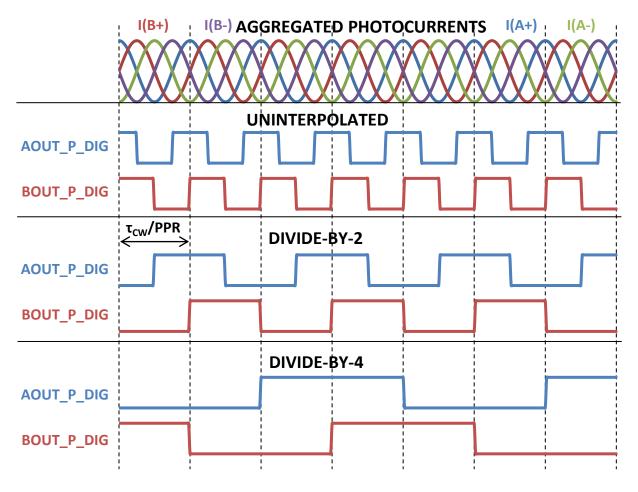

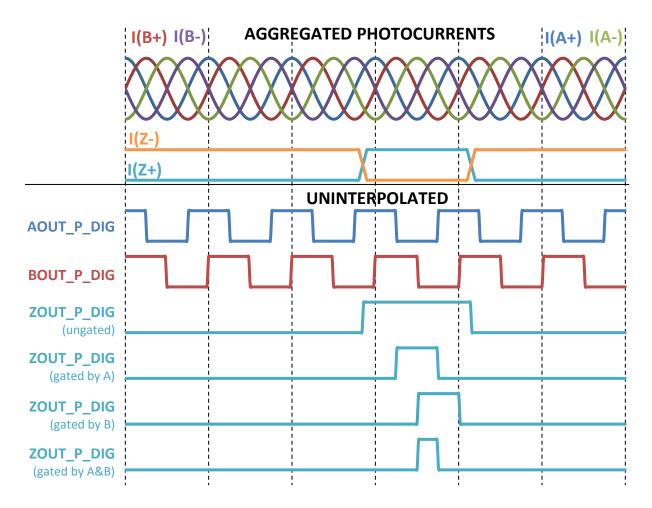

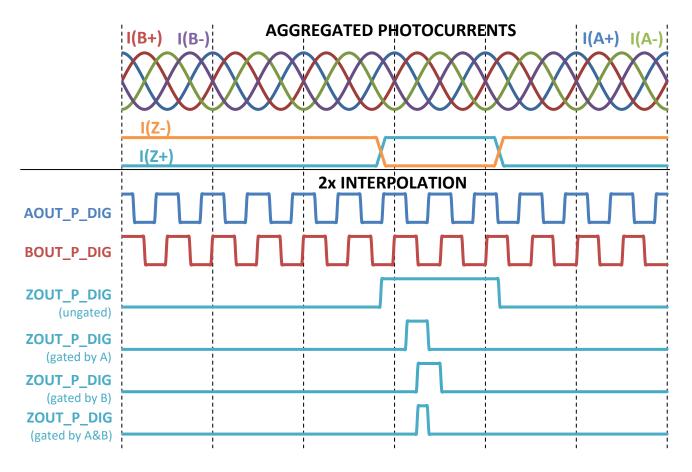

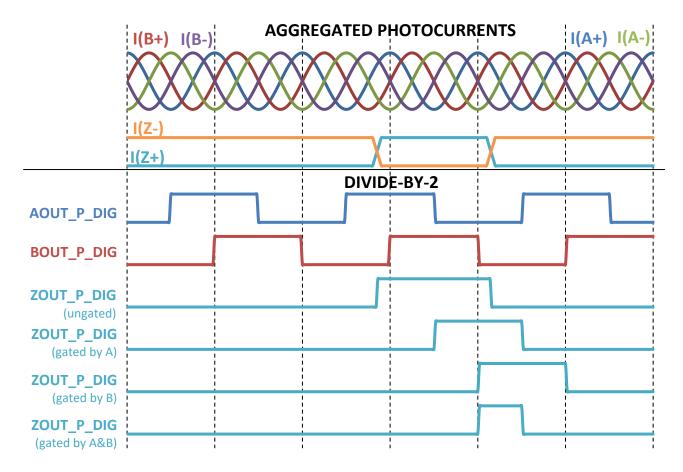

Figure 5 below shows the ideal response of the digital quadrature-track output pins (AOUT\_P\_DIG, AOUT\_N\_DIG, BOUT\_P\_DIG, BOUT\_N\_DIG) to constant-angular-velocity code-wheel rotation, with the FS210/FS310 configured for digital quadrature-track output. Four cases are shown: uninterpolated, 2x interpolation, 4x interpolation, and 8x interpolation. Fully differential outputs are shown in the uninterpolated case, but only the positive-sense signals are shown in the three interpolated cases. Even though they are not shown for all cases in the figure, when the device is configured for differential quadrature-track output, AOUT\_N\_DIG and BOUT\_N\_DIG are the logical complements of AOUT\_P\_DIG and BOUT\_P\_DIG, respectively, regardless of the configured interpolation factor. When the device is configured for single-ended digital quadrature-track output, then AOUT\_N\_DIG and BOUT\_N\_DIG are placed in a high-impedance state. When the device is configured for digital quadrature-track output – either differential or single-ended – then the analog quadrature-track output pins (AOUT\_P\_ANA, AOUT\_N\_ANA, BOUT\_P\_ANA, BOUT\_N\_ANA) are placed in a high-impedance state. In the Figure 5 and Figure 6,  $\tau_{CW}$  is the rotational period of the code wheel, and PPR is the number of native pulses per revolution in the code wheel's quadrature track.

Figure 6 below shows the ideal response of the positive-sense digital quadrature-track outputs to constant-angular-velocity code-wheel rotation, with the device configured for digital quadrature-track outputs, for three cases: uninterpolated, divide-by-2, and divide-by-4.

If the FS210/FS310 is configured for analog quadrature-track outputs, then the digital quadrature-track output pins (AOUT\_P\_DIG, AOUT\_N\_DIG, BOUT\_P\_DIG, BOUT\_N\_DIG) are placed in a high-impedance state, and the analog quadrature-track output (AOUT\_P\_ANA, AOUT\_N\_ANA, BOUT\_P\_ANA, BOUT\_N\_ANA) waveforms are similar to the aggregated photocurrent waveforms in the figure, centered at  $V_{0:Q} \approx 1.25V$  and multiplied by a common effective differential transimpedance.

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

Details of quadrature-track output-pin operation are controlled by the QCFG register as shown below:

### Quad-Track Configuration Register (QCFG: [0x0884]):

Table 10. QCFG register definition.

| MSB   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |  |

|-------|-------|-------|-------|-------|-------|-------|-----|--|

| SE_DZ | NB    | WL    | D_AZ  |       | INTP  |       |     |  |

Table 11. QCFG field description.

| Bits  | Definition                                                                                       |                                                    |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| INTP  | Digital interpolation or divide-down factor:                                                     |                                                    |  |  |  |  |  |

|       | 0000: No Interpolation                                                                           | <b>0001</b> : 2x multiply                          |  |  |  |  |  |

|       | <b>0010</b> : 4x multiply                                                                        | <b>0011</b> : 8x multiply                          |  |  |  |  |  |

|       | 0100: Reserved                                                                                   | <b>0101</b> : x2 divide                            |  |  |  |  |  |

|       | <b>0110</b> : x4 divide                                                                          | <b>0111</b> : x8 divide                            |  |  |  |  |  |

|       | <b>1000</b> : x16 divide                                                                         | <b>1001</b> : x32 divide                           |  |  |  |  |  |

|       | <b>1010</b> : x64 divide                                                                         | <b>1011</b> : x128 divide                          |  |  |  |  |  |

|       | <b>1100</b> : x256 divide                                                                        | <b>1101</b> : x512 divide                          |  |  |  |  |  |

|       | <b>1110</b> : x1,024 divide                                                                      | <b>1111</b> : x2,048 divide                        |  |  |  |  |  |

| D_AZ  | Analog/digital control for quadrature-track o                                                    | putputs                                            |  |  |  |  |  |

|       | <b>0</b> : Analog outputs                                                                        |                                                    |  |  |  |  |  |

|       | 1: Digital outputs                                                                               |                                                    |  |  |  |  |  |

| NBWL  | Reserved: Do not change from power-up de                                                         | fault (00)                                         |  |  |  |  |  |

| SE_DZ | Single-ended / differential digital output con                                                   | trol. (no effect if D_AZ bit is 0)                 |  |  |  |  |  |

|       | <b>0:</b> Differential (AOUT_P_DIG, BOUT_P_DIG, AOUT_N_DIG, BOUT_N_DIG all driven when D_AZ = 1) |                                                    |  |  |  |  |  |

|       | 1: Single-ended (AOUT_P_DIG and BOUT_<br>when D_AZ = 1)                                          | P_DIG driven; AOUT_N_DIG and BOUT_N_DIG not driven |  |  |  |  |  |

FS210/FS310 Datasheet

Figure 5: Quad-track outputs (Clockwise rotation; analog, digital 1x – 8x interpolation)

FS210/FS310 Datasheet

Figure 6: Quad-track outputs (Clockwise rotation; analog, digital uninterpolated, divide-by-2, -4)

## FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **Index-Track Outputs**

The digital index-track outputs ZOUT\_P and ZOUT\_N are intended to produce one single pulse per code-wheel revolution, provided the code wheel is designed properly for that purpose and the PXC/CCFG data pattern is consistent with the code wheel. ZOUT\_P is intended to be low for most of the code-wheel revolution and to have a single high-going pulse once per revolution. ZOUT\_N is the logical complement of ZOUT\_P and therefore is intended to be high for most of the code-wheel revolution and to have a single low-going pulse once per revolution, coincident with the single high-going pulse on ZOUT\_P.

The Index-Track Configuration Register ZCFG controls whether the index-track output is differential – i.e. both ZOUT\_P and ZOUT\_N to complementary logic levels – or single-ended – i.e. the FS210/FS310 places ZOUT\_N in a high-impedance state and only drives ZOUT\_P. ZCFG also controls the timing of the single pulse on ZOUT\_P/ZOUT\_N with respect to the quadrature-track outputs.

Additionally, ZCFG contains a bit that affects the quadrature-track signal path: The power-on default state (0) of the TLNM bit allows for analog quadrature-track signal frequencies as high as 1MHz, but with comparatively low transimpedance, so a comparatively higher buffer gain is required in order to achieve adequate signal amplitude, which also gains noise and therefore degrades signal quality. In low-noise mode (TLNM = 1), the quadrature-track transimpedance is comparatively higher, so less buffer gain is needed, producing less output-referred noise and better signal quality, but at the cost of limiting the analog quadrature-track signal frequency to no more than 400kHz.

#### **Index Track Gating**

The ZOUT signals can optionally be gated by the quadrature outputs as detailed in the section below. All the gating features are defined with  $Z_+$  -  $Z_-$  tracks are greater than 0 and  $X_+$  -  $X_-$  is less than 0, where X is either A or B as chosen in the ZCFG register. If the opposite polarity of the quadrature signal is desired, i.e.  $X_+$  -  $X_-$  is greater than 0, please contact the factory.

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### Index-Track Configuration Register (ZCFG: [0x0885]):

Table 12. ZCFG register definition

| MSB  | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|------|------------|-------|-------|-------|-------|-------|-----|

| RSVD | TLNM ('b1) | RSVD  |       | SE_DZ | RSVD  | ZGCTL |     |

Table 13. ZCFG field description

| Bits  | Description             | Description                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ZGCTL | Index-pulse gati        | ng control:                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|       | <b>00</b> : Ungated     | ZOUT_P = 1 when Z+ aggregated photocurrent is greater than Z- aggregated photocurrent, regardless of quadrature-track output condition                                                                                                                                                                 |  |  |  |  |  |

|       | <b>01</b> : Gated by A  | ZOUT_P = 1 beginning at the first AOUT_P_DIG falling edge after Z+ aggregated photocurrent becomes greater than Z- aggregated photocurrent and ending at the next subsequent AOUT_P_DIG rising edge                                                                                                    |  |  |  |  |  |

|       | 10: Gated by B          | ZOUT_P = 1 beginning at the first BOUT_P_DIG falling edge after Z+ aggregated photocurrent becomes greater than Z- aggregated photocurrent and ending at the next subsequent BOUT_P_DIG rising edge                                                                                                    |  |  |  |  |  |

|       | <b>11</b> : by A & B    | ZOUT_P = 1 beginning at the first AOUT_P_DIG falling edge when BOUT_P_DIG = 0 or the first falling BOUT_P_DIG falling edge when AOUT_P_DIG = 0 after Z+ aggregated photocurrent becomes greater than Z- aggregated photocurrent and ending at the next subsequent AOUT_P_DIG or BOUT_P_DIG rising edge |  |  |  |  |  |

| SE_DZ | Single-ended/di         | fferential output control:                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|       | <b>0</b> : Differential | Device drives ZOUT_P, ZOUT_N to complementary logic levels                                                                                                                                                                                                                                             |  |  |  |  |  |

|       | 1: Single-ende          | d Device places ZOUT_N in high-impedance state and only drives ZOUT_P                                                                                                                                                                                                                                  |  |  |  |  |  |

| TLNM  | Always set to 'b        | 1:                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|       | 1: Low-Noise            | Quad-track signal path has 3dB corner frequency limited to 400KHz                                                                                                                                                                                                                                      |  |  |  |  |  |

| RSVD  | Reserved for fut        | ure use                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

### FlexSense® I-Series Programmable **Incremental Encoder**

The figures below depict ideal index-track output responses for a variety of combinations of code-wheel rotation direction, gating, and interpolation settings.

Figure 7: Index-Track Output Response (A leading B, digital, uninterpolated)

FS210/FS310 Datasheet

Figure 8: Index-Track Output Response (A leading B, digital, 2x interpolation)

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

Figure 9: Index-Track Output Response (A leading B, digital, divide-by-2)

FS210/FS310 Datasheet

### **Signal Conditioning**

For ideal system-level determination of position and velocity, the sinusoidal quadrature-track analog voltages produced from the aggregated photocurrents from the FS210/FS310's properly-configured pixel array should have zero DC offset and equal amplitudes and be exactly 90° out of phase. Deviations from these ideal signal characteristics can arise from several sources, such as:

- Mismatch between the LED's emission pattern, the code wheel, and the PXC/CCFG pattern

- Imperfections in code-wheel printing

- Code-wheel eccentricity and/or presence of an out-of-plane component of rotation

- Transistor-level mismatches in the FlexSense<sup>™</sup> chip

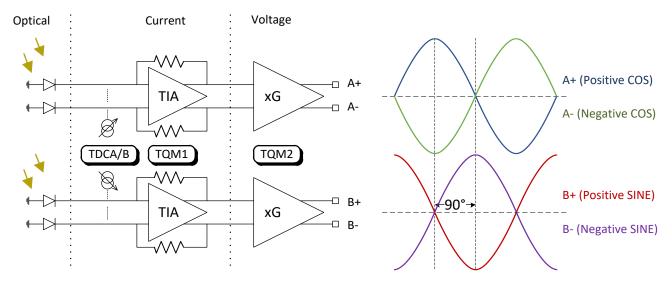

The FS210/FS310 contains registers to trim the quadrature-track DC offsets and amplitudes. below illustrates the quadrature-track signal path. The nominal value of the TIA feedback resistors is  $230k\Omega$  if the TLNM bit in the ZCFG control register is 0, or  $700k\Omega$  if the TLNM bit is 1. The power-on default voltage gain of the second-stage buffer is 4.

Figure 10: Differential Photocurrents (A+/A- & B+/B-) Signal paths

A small current can be injected in parallel with either the A+ or the A- aggregated photocurrent, and another small current can be injected in parallel with either the B+ or the B- aggregated photocurrent. The TDCA and TDCB trim registers, respectively, control these currents. Adding trim current in parallel with the A+ (B+) aggregated photocurrent acts to make the DC offset of the A (B) differential output voltage more positive or less negative. Adding trim current in parallel with the A- (B-) aggregated photocurrent acts to make the DC offset of the A(B) differential output voltage less positive or more negative. Up to 31 steps of 4nA each can be added to either the A+ or the A- aggregated photocurrent, and up to 31 steps of 4nA each can be added to either the B+ or the B- aggregated photocurrent.

Mismatches in the amplitudes of the A+/A- and B+/B- differential output voltages can be counteracted by reducing the feedback transresistances around whichever of the A or B transimpedance amplifier produces a greater untrimmed differential sinusoidal voltage amplitude. The TQM1 trim register controls this transimpedance attenuation: one bit selects either the A or B transresistances to be attenuated, and the remainder of the register allows the selected transresistances to be reduced by up to 7 steps of 5% each.

# FlexSense® I-Series Programmable Incremental Encoder

Finally, the voltage gain of the second-stage buffers in both the A and B paths can be changed under the control of the TQM2 trim register. The buffer gain can be set to 4 (power-up default), 6, 8, 12, 16, 24, 32, 48 or 64. Changing the TQM2 setting changes the gains of both the A+/A- buffer and the B+/B- buffer together.

#### Offset Trim Register A (TDCA: [0x0880])

#### Table 14. TDCA register definition

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|-----|-------|-------|-------|-------|-------|-------|-----|

| RS  | VD    | SDCA  |       | MDCA  |       |       |     |

#### Table 15. TDCA field description

| Bits | Description                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDCA | Magnitude: 4nA/LSB added to A+/A- transimpedance amplifier input selected by SDCA bit                                                                                                                                                             |

| SDCA | Sign bit: Selects whether extra current is to be added to positive- or negative-sense aggregated photocurrent input to A+/A- transimpedance amplifier  0: Add current to A- aggregated photocurrent  1: Add current to A+ aggregated photocurrent |

| RSVD | Reserved for future use                                                                                                                                                                                                                           |

#### Offset Trim Register B (TDCB: [0x0881])

#### Table 16. TDCB register definition

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|-----|-------|-------|-------|-------|-------|-------|-----|

| RS  | VD    | SDCB  |       |       |       |       |     |

#### Table 17. TDCB field description

| Bits | Description                                                                                                                                                                                                                                       |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MDCB | Magnitude: 4nA/LSB added to B+/B- transimpedance amplifier input selected by SDCA bit                                                                                                                                                             |  |  |  |  |

| SDCB | Sign bit: Selects whether extra current is to be added to positive- or negative-sense aggregated photocurrent input to B+/B- transimpedance amplifier  0: Add current to B- aggregated photocurrent  1: Add current to B+ aggregated photocurrent |  |  |  |  |

| RSVD | Reserved for future use                                                                                                                                                                                                                           |  |  |  |  |

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### Magnitude Trim Register 1 (TQM1: [0x0882])

#### Table 18. TQM1 register definition

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |  |

|-----|-------|-------|-------|-------|-------|-------|-----|--|

|     | RSVD  |       |       |       | MQM1  |       |     |  |

#### Table 19. TQM1 field description

| Bits | Description                                                                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MQM1 | Magnitude: Feedback transimpedance resistance around selected TIA reduced by 5%/LSB                                                                               |

| SQM1 | Select bit: Selects the TIA whose feedback transresistances should be reduced  O: Reduce B+/B- feedback transresistance  1: Reduce A+/A- feedback transresistance |

| RSVD | Reserved for future use                                                                                                                                           |

### Magnitude Trim Register 2 (TQM2: [0x0883])

#### Table 20. TQM2 register definition

| MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |  |  |

|-----|-------|-------|-------|-------|-------|-------|-----|--|--|

|     | RSVD  |       |       |       | MQM2  |       |     |  |  |

#### Table 21. TQM2 field description

| Bits | Description                                              |                        |                        |  |  |  |

|------|----------------------------------------------------------|------------------------|------------------------|--|--|--|

| MQM2 | Magnitude: Identically sets A+/A- and B+/B- buffer gains |                        |                        |  |  |  |

|      | <b>0000:</b> Gain = 4                                    | <b>0011:</b> Gain = 12 | <b>0110:</b> Gain = 32 |  |  |  |

|      | <b>0001:</b> Gain = 6                                    | <b>0100:</b> Gain = 16 | <b>0111:</b> Gain = 48 |  |  |  |

|      | <b>0010:</b> Gain = 8                                    | <b>0101:</b> Gain = 24 | <b>1xxx:</b> Gain = 64 |  |  |  |

| RSVD | Reserved for future use                                  |                        |                        |  |  |  |

## FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

### **LED Drive Control**

The LEDK pin of the FS210/FS310 is intended to be connected to the cathode of the LED acting as the light source for the encoder system. The LED is external for the FS210 and is in-package for the FS310. The LED drive can be regulated either at a fixed current level or in a closed control loop, as selected by bit 7 of the ILED control register. The drive current can be disabled completely by writing the ILED control register to 0x00.

In a transmissive-mode design the LED is placed on the opposite side of the code wheel from the PCB containing all the other components in the encoder module, with the LEDK pin of the FlexSense<sup>TM</sup> device connected off-board to the cathode of the LED. The OP207CL IR LED from TT Electronics is recommended for use with the FS210.

In open-loop control, the current sunk by the LEDK pin is kept first-order constant at the level coded by the least-significant 7 bits of the ILED control register. ILED<6:0> is taken to represent an unsigned binary-weighted integer in the range [0, 127], and the drive current is fixed at 0.6mA/LSB nominally. Therefore, the optical power density incident to the FS210/FS310 varies directly with the LED optical output power at this fixed drive current – both with temperature (LED optical output power at a given drive current decreases with increasing temperature and vice-versa) and with LED degradation (LED optical output power at a given drive current at constant temperature decreases slowly over the operating lifetime of the LED).

In closed-loop control, the current sunk by the LEDK pin is varied in order to maintain nearly constant quadrature-track signal voltage amplitude at all operating conditions – i.e. to compensate automatically for the degradation of LED output optical power over operating life and for the heavy negative temperature dependence of LED output optical power at a given drive current – without requiring any explicit user action. At the onset of closed-loop control, the LEDK drive current is initialized to 7/8 (0.875) of the value encoded by ILED<6:0>. The LEDK drive current is decreased by 0.6mA if the quadrature-track differential output voltage amplitude is greater than the level encoded by the LEDLP control register, and the LED drive current is increased by 0.6mA if the quadrature-track differential output voltage amplitude is less than the level encoded by LEDLP and the drive current does not exceed the level encoded by ILED<6:0>. In no case can the LEDK drive current be greater than the level encoded by ILED<6:0>. The LEDK drive current is updated approximately either once every sixteen seconds or once every second, depending on the state of the FAST bit of the LEDLP control register. The value of the actual LEDK drive current can be read back through the LEDLV status register.

In closed-loop control, if the actual LEDK drive current is greater than 7/8 of the level encoded by ILED<6:0>, an alarm condition is present: bit 6 of the interrupt mask/status register is set, and an interrupt is generated if not masked by bit 2 of the interrupt mask/status register.

#### LED Drive Current Control Register (ILED: [0x0886])

### Table 22. ILED register definition

| MSB  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|------|-------|-------|-------|-------|-------|-------|-----|

| C_OZ |       |       |       | ILK   |       |       |     |

General Note

# FlexSense® I-Series Programmable Incremental Encoder

FS210/FS310 Datasheet

Table 23. ILED field description

| Bits | Description                                                                                                                                          |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ILK  | Binary-weighted LEDK drive current (actual if C_OZ = 0, maximum if C_OZ = 'b1); 0.6mA/LSB nominally                                                  |  |  |  |  |  |

| C_OZ | Open/Closed loop current control bit:                                                                                                                |  |  |  |  |  |